人工智能研究院唐希源课题组在面向边缘传感器的数据转换器方向的研究取得进展

2023/04/20 信息来源: 人工智能研究院

编辑:麦洛 | 责编:山石北京大学人工智能研究院类脑智能芯片研究中心唐希源研究员课题组在ISSCC 2023会议上发表论文“A 150kHz-BW 15-ENOB Incremental Zoom ADC with Skipped Sampling and Single Buffer Embedded Noise-Shaping SAR Quantizer”,发布了一种最新研制并实现的增量型缩放式模数转换器芯片,这款芯片在相似性能的增量型模数转换器中具有最高的输入带宽(150kHz)和最小的输入驱动要求(6.4pF/conv.),其能效达到182.2dB FoM。

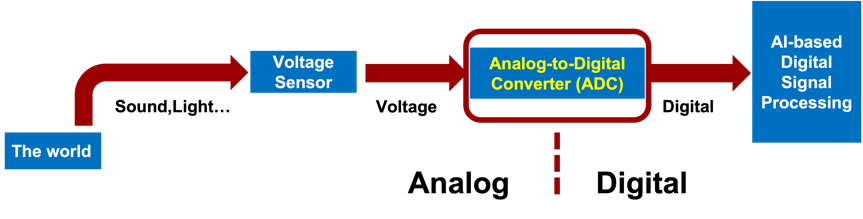

随着人工智能技术的飞速发展和集成电路性能的不断进步,越来越多智能物联网设备被广泛应用于各个领域,如语音识别、健康检测等。这些应用推动着人类社会朝更加智能化的方向迈进,给人们的生活带来极大便利。对于部署到真实世界的边缘端智能物联网设备,它对真实世界的声音、图像乃至生物电等信号(模拟信号)的感知和探测都需要依靠传感芯片来进行。模数转换器(ADC)作为边缘端传感芯片中的核心部件,承担了跨接在模拟域与数字域之间的桥梁作用(图1)。

图1. 边缘端智能传感系统

在边缘端的传感芯片中,首先需要通过模数转换器将这些外部世界的模拟信号转换为数字信号,再将转换后的数字信号输送给计算平台进行处理、分析并决策,模数信号的转换精确度对整个传感芯片的工作结果产生重要影响。因此,高精度、高能效并能支持中等输入带宽的模数转换器成为先进边缘端传感芯片的关键部分。

缩放式模数转换器(Zoom ADC)是物联系统中一种流行的模数转换器结构。其首先采用一个高能效的SAR量化器对采样输入进行粗量化,再用一个高精度的Delta-Sigma量化器对粗量化后的余差进行细量化,从而同时满足高精度和高能效的性能需求。然而传统的Delta-Sigma量化器工作模式会破坏余差信息,从而需要大量的重复采样进行余差重建。该操作大幅增加了模数转换器的驱动开销,对系统集成提出挑战。此外,它还严重限制了转换速度,传统Zoom ADC只能转换直流或者低频输入信号,难以满足先进传感芯片对模数转换器带宽的需求。

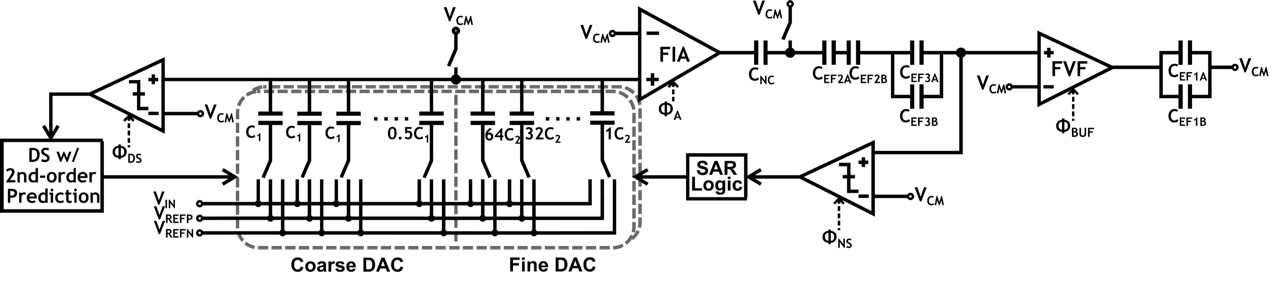

针对上述缩放式模数转换器设计面临的带宽和驱动需求的挑战,唐希源课题组从缩放式模数转换器的架构和电路方面进行创新,提出了新的设计方法来解决这些挑战(图2)。

图2. 提出的缩放式模数转换器电路结构图

在架构方面,该工作采用噪声整形SAR量化器进行缩放式模数转换器中的细量化,利用SAR多比特量化的特点设计出缩放式模数转换器,降低了高精度转换所需的次数。另外,该工作首次提出跳跃采样技术,在新提出的架构中,细量化过程不再会破坏余差电压,因此一次采样后可以进行多次连续的细量化而不再需要重复采样,从而降低了对采样电路的要求,并提升了系统的带宽。

在电路方面,该工作提出了一种新型的环路滤波器电路设计方法,该方法仅需要一个动态缓冲器和若干电容即可实现高阶、高鲁棒性的环路滤波器,显著降低了系统硬件开销和功耗。

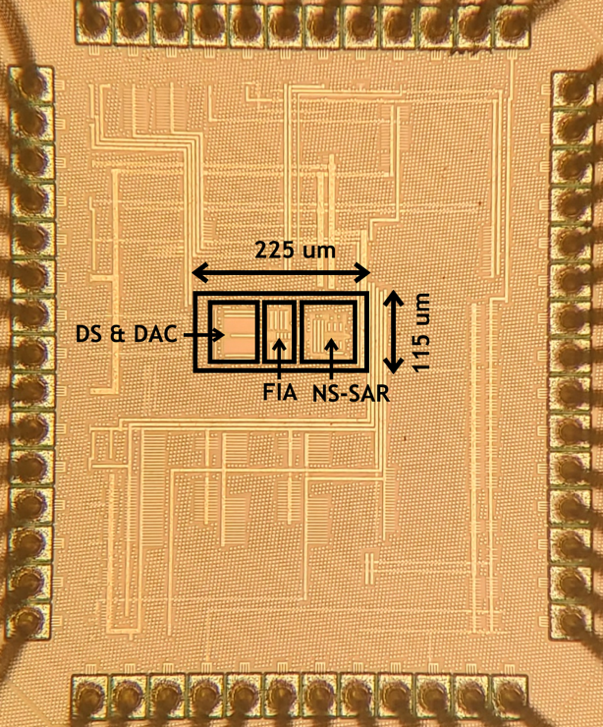

基于上述创新技术,课题组研制并实现了一款基于28nm CMOS工艺的增量型缩放式模数转换器芯片(图3)。

图3. 28nm芯片原型显微图

这款芯片大幅降低模数转换所需采样操作的频次,能够实现150kHz的转换带宽,输入驱动要求为6.4pF/步,在2.5kHz和20kHz的输入信号下分别达到92.5dB和92.2dB的信噪失真比,系统功耗仅为160uW,实现了182.2dB的品质因数)。该芯片可广泛应用于包括语音、监测等多种边缘端传感场景。

北京大学博士研究生王宗楠为第一作者,唐希源为通讯作者。

转载本网文章请注明出处